- TESTING LADDER LOGIC PROGRAM VERIFICATION

- TESTING LADDER LOGIC PROGRAM SOFTWARE

- TESTING LADDER LOGIC PROGRAM CODE

- TESTING LADDER LOGIC PROGRAM SIMULATOR

TESTING LADDER LOGIC PROGRAM CODE

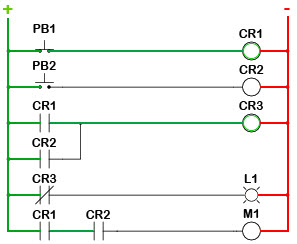

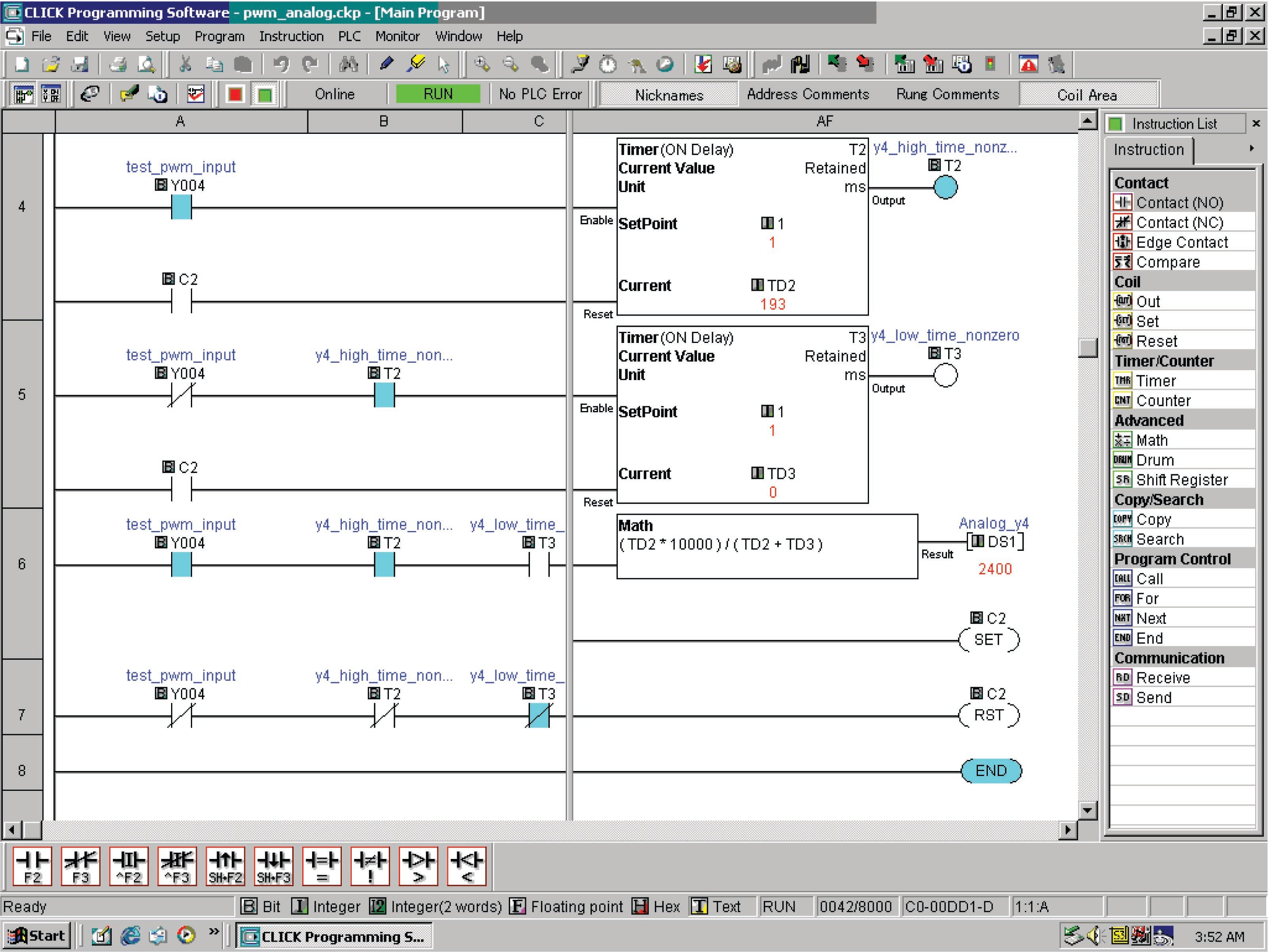

This work is done using a general purpose program analysis and transformation tool calledĭMS used to instrument the RLL code with additional logic to collect the necessary data. This tells, for each condition in rung, whether that condition has been tested as TRUE, tested as FALSE, and more importantly, if there the condition controlled the output of the decision in the rung (well at least the action controlled by the decision) in both true and false directions under some test. What we have prototyped is MC/DC (modified/condition/decision coverage) for RLL code for Rockwell controllers. A PLC has many input terminals, through which it interprets high and low logical states from sensors and switches. Most procedural language test coverage tools do branch coverage or some such because Relay Ladder Logic typically doesn't branch, this doesn't work very well.

First students work through an introductory lab on PLC programming to introduce them to the PLC hardware, the PLC programming environment and the basics of ladder logic.

We've experimented with test coverage tools for Rockwell Control Logix controllers. AbstractThis paper describes a Programmable Logic Controller (PLC) lab component that has been added to the last three weeks of a digital logic semester-based course. Here is one that runs on windows supposedly: There are a couple of ladder logic editors (with simultors) available for free. Sorry, I have never looked for ladder logic to/from verilog translators.īut ladder logic in my day was only just being put into a computer for programming PLC's - most of the relay systems I used were REAL Relays, wired into the cabinets!! It may be helpful to program in some unit delays. Simulation mode allows you to test your program in WindLDR to guarantee. Verilog will be an easier language to develop your tests and testbenches in! Use the tag editor to access and edit coil data. (Note: in Ladder Logic for PLC convention, Rnn is for internal relays, while, Xnn is an input and Ynn is an output, as can be quickly gleaned from one of the online tutorials.

TESTING LADDER LOGIC PROGRAM SOFTWARE

Make sure you're testcases give good CODE coverage of your logic! And If your ladder editing software gives you decent naming capabilities, use them, rather than Rnn.

TESTING LADDER LOGIC PROGRAM SIMULATOR

Then use a free verilog simulator like Icarus to develop a testbench and test your system. A model is constructed mechanically from the ladder logic program and. Or you could use an assign statement assign R18 = R16 & (R15 | R12) Ī latching relay assign R18 = (set condition) || R18 & !(break condition) Control system programs are usually validated by testing prior to their deployment. To an expression like always R18 = !R16 & ( R15 | R12) Ladder logic can be transformed to one of the modern HDL's like Verilog.

TESTING LADDER LOGIC PROGRAM VERIFICATION

0 kommentar(er)

0 kommentar(er)